Barrel Shifter

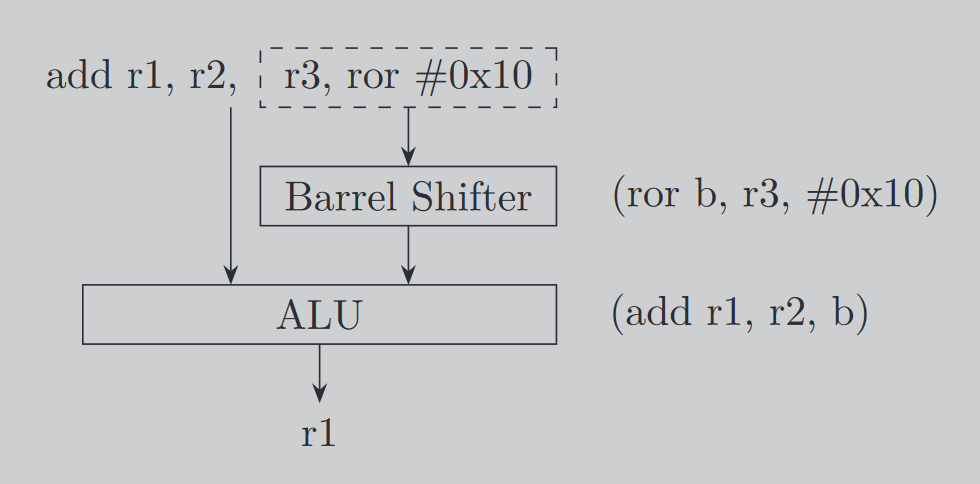

The inline barrel shifter feature, also known as the constant shift feature, allows to optionally shift the Rn operand for most instructions before it is processed by the main instruction. This is a hallmark feature of ARM processors and is widely used in optimization by programmers and compilers alike.

When an instruction includes a shift to its Rn operand, this is evaluated first.

For example add r1, r2, r3 ror #0x10 should be interpreted as r1 = r2 + ror(r3, 0x10).

Comparison between using separate bit-shifting instructions and using the barrelshifter.

sample_a:

ror r3, #0x10

lsr r4, #8

add r1, r2, r3

orr r1, r4

bx lrDiscrete rotate and shift instructions.

sample_b:

add r1, r2, r3, ror #0x10

orr r1, r1, r4, lsr #8

bx lrRotate and shift instructions using the barrel shifter.

The example above depicts the same calculation performed with and without the use of the barrelshifter. Shifting an operand does not add any cycles, thus it can be used to eliminate the cycles used by shift instructions. The performance impact can be seen in the table below.

Benchmark results of bit-shifting examples

| Figure | sample a | sample b |

|---|---|---|

| Instructions executed | 4 | 2 |

| LSU count | 0 | 0 |

| CPI count | 0 | 0 |

| Fold count | (-) 0 | (-) 0 |

| Cycle count | 4 | 2 |